Chip Interconnect Solution

신호 신뢰성 평가를 위한 High-Speed Interconnect 시스템 시뮬레이션 플랫폼 개발

- Seoul National Univ, Samsung Cluster Project ( 2021. 06 ~ )

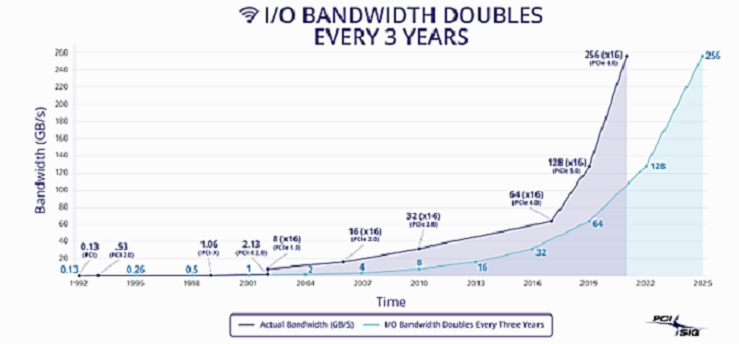

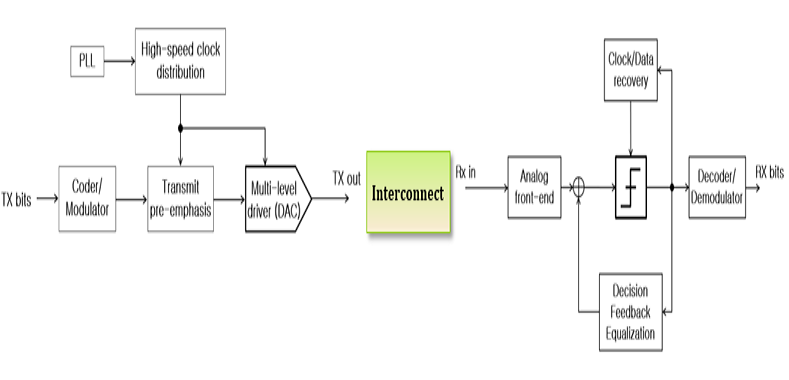

본 연구는 신호 신뢰성 평가를 위한 고속 인터페이스 시스템 설계 플랫폼을 개발하고, 머신러닝을 활용한 인터커넥트 시스템 성능 최적화 기술로의 확장을 목표로 한다. 오늘날의 고속 I / O 인터페이스는 채널 손실을 보상하기 위해 최적의 이퀄라이저를 설계하고, 다른 Clocking System을 비교하고, 디지털 교정 / 적응 루프의 기능을 검증하기 위해 광범위한 모델링 및 시뮬레이션이 요구된다. 따라서, 고속 인터페이스 시스템 성능 분석을 위해서는 각 링크 구성 요소에 대한 주요 모델링 요구 사항을 이해하고, 높은 정확도와 빠른 속도를 모두 달성할 수 있는 효율적인 시뮬레이터를 사용한다. 또한 Machine Learning 기반 채널 시뮬레이션 기술을 개발하여 고속 동작 시 인터커넥에서 일어나는 손실과 반사를 eye-diagram 예측에 활용한다. 본 연구에서 개발하는 시뮬레이션 플랫폼은 인공지능을 사용한 성능 개선이나 설계 자동화로 확장이 가능하게 구축한다. 그리고, Signaling(Coding) 방식의 변화에 따른 신호 신뢰성, 전력 소모, 설계 효율을 평가할 수 있도록 한다.

High-Speed Interconnect

머신 러닝을 사용한 인터커넥트 설계 플랫폼 개발

- 한국 연구재단 중견연구 ( 2020.3 ~ )

본 연구는 고속신호가 전송되는 인터커넥트와 신호전송 방식에 머신러닝을 적용하여, 최적의 신호무결성 및 EMC 성능을 가지도록 하는 인터커넥트 설계 플랫폼을 개발하는 것을 목표로 한다. 시스템의 고속화와 소형화에 대응하기 위해 인터커넥트는 다양한 매질과 구조로 설계되는데, 머신러닝을 이용하여 기하학적 구조, 속도, 매질 등의 설계 변수와 신호 신뢰성, 전력소모, EMC 등의 성능 지표 사이의 연관을 묘사하는 네트위크를 생성하고, 이를 이용하여 목표 사양을 만족하는 구조를 설계할 수 있는 플랫폼을 개발한다. 머신러닝을 통해 기존의 설계 방식 대비 설계 시간을 단축하는 것을 목표로 한다.

Advanced Field-Effect Transistor Desgin

ML 기반 효율적인 Device Compact Model Framework 개발

- Institute for Information & communication Technology Planning & evaluation (IITP) ( 2021.04 ~ )

차세대 소자에 대한 Machine Learning 기반의 효율적인 Device Compact Model Framework을 개발하고, Device Compact Model의 학습 효율 개선 및 정합성 향상을 목표로 한다. 또한 Machine Leaning을 기반으로 한 Design Technology Co-Optimization(DTCO) 기술을 개발하여 차세대 공정에 적용 가능한 Machine Learning 기반의 대표적 Cell 최적 설계 평가 기술을 구현한다.

.

KAIST, POSTECH, Seoul National Univ, Sungkyunkwan Univ, Yonsei Univ, Hanyang univ, Chengju Univ, Incheon Univ, BAUM, EnableDesign